AMD is said to use 15 metal layers that are optimized for both high frequencies and the ability to achieve high transistor density. The density of transistors in the 5nm part of the processors is therefore on average over 90 million per mm². But it contains 6.57 billion transistors, 58 % more than the Zen 3 generation chiplet (which was claimed to have 4.15 billion transistors in 83.74 mm²).

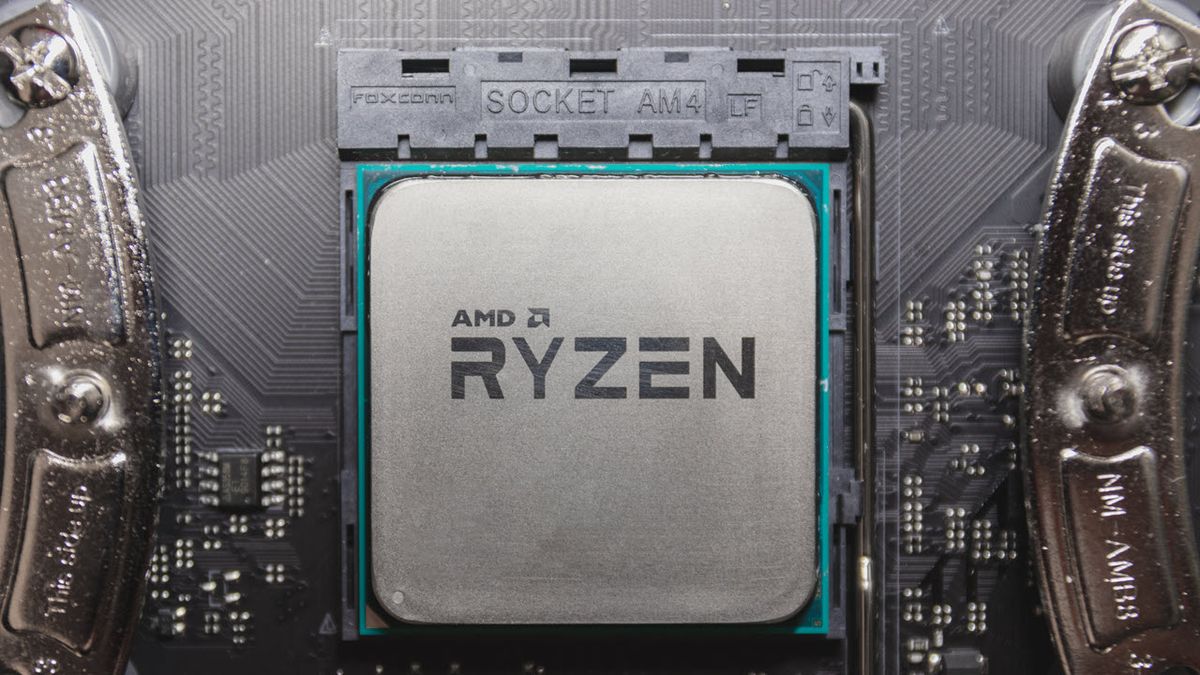

The Durago chiplet is more than 10 % smaller than the Zen 3 core chiplet in Ryzen 5000, occupying an area of just 71 mm², according to AMD. The Zen 4 CPU core architecture then has the codename “Persephone”. But the CPU chiplet itself has reportedly its own codename (Durango) at AMD, so you may see that referenced in the future. Up until this point, we’ve known the entire Ryzen 7000 under the codename “Raphael”. These are then connected to a 6nm central IO die. 5nm chiplet DurangoĪs has been known for some time, Zen 4 is manufactured on TSMC’s 5nm process (N5) – more specifically, this technology is used to produce CPU chiplets, which are relatively small silicon dies containing the Zen 4 cores and their 元 cache. So let’s have a deeper look at Zen 4 architecture, the 5nm chiplets of the processors and finally the core’s IPC – which has actually improved more than the previously promised +8 to 10 % over Zen 3. The company has also disclosed a considerable amount of technical details and more has now leaked from unofficial sources.

Zen 4's IPC is actually better than what AMD originally saidĪMD formally launched the Ryzen 7000 (with availability four weeks away though) and confirmed specs and pricing.

0 kommentar(er)

0 kommentar(er)